Author: Oscar Mansilla

## ISL705XRH Evaluation Board User's Guide

## Introduction

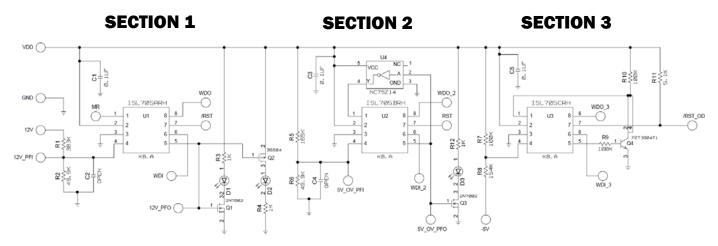

The ISL705XRHEVAL1Z evaluation board is a design platform featuring all three versions of the 5V supervisory circuit. It includes all the circuitry needed to characterize critical performance parameters and enables evaluation of basic functional operation and common application implementations. Figure 1 shows the ISL705XRHEVAL1Z schematic.

## **Evaluation Board Key Features**

The ISL705XRHEVAL1Z is divided into three sections; each section having one of the three available reset output versions. The left position has the ISL705ARH and is set-up as a +12V and +5V UV monitor with reset signal. The middle position features the ISL705BRH set up as 5V window detector. The right section contains the ISL705CRH in a bipolar voltage sensing application.

#### **Section 1**

In the first section, the ISL705ARH is configured to monitor under voltage conditions on a +5V supply through the  $V_{DD}$  pin and on a +12V supply through the PFI pin. The PFI allows monitoring of any voltage above the 1.25V PFI reference, and, with a resistor divider, this is used to monitor the +12V. The rising threshold for the +12V auxiliary voltage is set to 10.84V via the R1, R2 divider. When this condition is met, PFO will be high driving on a green LED. When the +12V auxiliary voltage falls below 10.84V, PFO is pulled low and a red LED will be turned on. The active low reset signal may be monitored through the  $\overline{\text{RST}}$  test point. There is also a  $\overline{\text{MR}}$  test point in order to drive the MR low to test its functionality.

#### **Section 2**

The middle position has the ISL705BRH installed and is set-up as a 5V window detector. The  $V_{DD}$  monitors for UV and the PFI for OV via the R5, R6 divider. The PFO output is inverted and connected to the manual reset input (MR) via U4. Hence, a reset signal is generated when 4.64V <  $V_{DD} > 5.38$ V. Without U4, the PFO will be an OV indicator but no reset signal will be generated. There is also a LED indicator for an overvoltage condition, when  $V_{DD} > 5.38$ V PFO is a high and a LED will turn on indicating an OV condition. The active high reset signal for a UV condition may be monitored through the RST test point.

#### **Section 3**

The right position features the ISL705CRH in a negative voltage sensing application. A +5V supply is monitored through the  $V_{DD}$  pin and a -5V supply is monitored on the PFI pin with use of the R7, R8 resistor divider network. Both pins are sensing for an undervoltage condition. When the -5V supply rail drops below -4.5V, PFO will be high driving on the N3904 NPN transistor. As the NPN turns on, the manual reset  $(\overline{\text{MR}})$  pin will be pulled low, initiating a reset. A UV condition may be monitored on the  $\overline{\text{RST}\_\text{OD}}$  pin, which has a  $5.1\text{k}\Omega$  pull-up resistor to  $V_{DD}$ .

## **Watchdog Timer Functionality**

All of these positions have independent Watchdog input (WDI) and Watchdog output (WDO) test points to evaluate the functionality of the watchdog timer. A waveform generator may be used to apply a square wave signal to the WDI test points and the output monitored through the WDO test points. The WDI may also be left open and WDO is now a low line indicator of the voltage on  $V_{DD}$ .

# **Power Supplies**

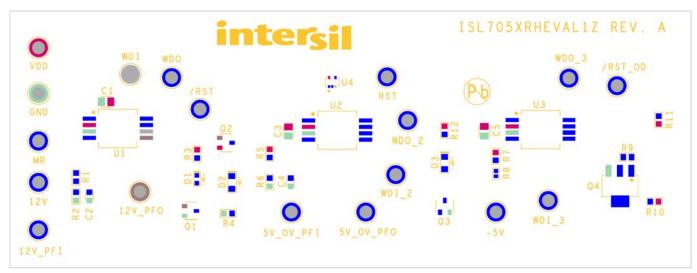

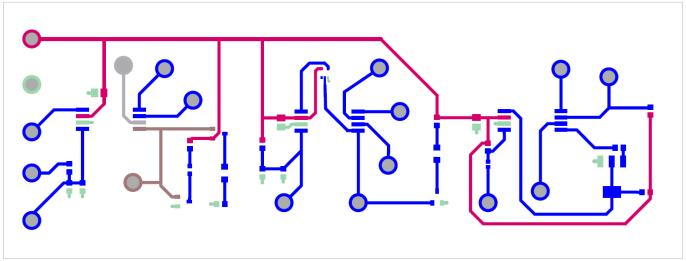

External power connections are made through the VDD, 12V, -5V and Ground connections on the evaluation board. All three sections share a common VDD test point with a decoupling capacitor C1. The PFI pins in section 1 and 2 have a unpopulated component pad to add decoupling capacitors C2 and C3 if needed.

## **Reference Documents**

ISL705ARH, ISL705BRH, ISL705CRH, ISL706ARH, ISL706BRH, ISL706CRH Datasheet, FN7662

# **Application Note 1650**

FIGURE 1. ISL705XRHEVAL1Z SCHEMATIC

# **Bill of Materials**

TABLE 1. ISL705XRHEVAL1Z COMPONENTS PARTS LIST

| DEVICE #    | DESCRIPTION                                         | COMMENTS                                   |

|-------------|-----------------------------------------------------|--------------------------------------------|

| C1, C3, C5  | CAP, SMD, 0603, 0.1µF, 50V, 10%, X7R, R0HS          | Power Supply Decoupling                    |

| C2, C4      | CAP, SMD, 0603, DNP, ROHS                           | User selectable capacitors - not populated |

| D1, D2, D3  | LED, SMD, ROHS                                      | Power Fail Indicator                       |

| Q1, Q3      | N-Channel EMF Effect Transistor, SMD, SOT-23,ROHS   | Power Fail Detector                        |

| Q2          | P-Channel EMF Effect Transistor, SMD, SOT-23,ROHS   | Power Fail Detector                        |

| Q4          | NPN General Purpose Transistor, SMD, S0T-223, ROHS  |                                            |

| R1          | RES, SMD, 0603, 383k $\Omega$ , 1/16W, 1%, ROHS     | PFI Voltage Divider Network                |

| R2, R6      | RES, SMD, 0603, 49.9kΩ, 1/10W, 1%, ROHS             | PFI Voltage Divider Network                |

| R3, R4, R12 | RES, SMD, 0603, 1kΩ, 1/10W, 1%, ROHS                | LED Current Limiting Resistor              |

| R5          | RES, SMD, 0603, 165k $\Omega$ , 1/16W, 1%, ROHS     | PFI Voltage Divider Network                |

| R7, R9, R10 | RES, SMD, 0603, 100kΩ, 1/16W, 1%, ROHS              | PFI Voltage Divider Network                |

| R11         | RES, SMD, 0603, 5.1kΩ, 1/16W, 1%, ROHS              | ISL705CRH Reset Pull-up Resistor           |

| U1          | ISL705ARH, 8 Ld Flatpack, 5V Supervisory Circuit    |                                            |

| U2          | ISL705BRH, 8 Ld Flatpack, 5V Supervisory Circuit    |                                            |

| U3          | ISL705CRH, 8 Ld Flatpack, 5V Supervisory Circuit    |                                            |

| U4          | UHS Inverter with Schmitt Trigger Input, SC70, ROHS |                                            |

# **Application Note 1650**

FIGURE 2A. ISL705XRHEVAL1Z TOP SILK SCREEN

FIGURE 3A. ISL705XRHEVAL1Z TOP VIEW

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.